# References for A/D Converters

National Semiconductor Application Note 184 July 1977

Interfacing between digital and analog signals is becoming increasingly important with the proliferation of digital signal processing. System accuracy is often limited by the accuracy of the converter and a limitation of the converter is the voltage reference. Design can be difficult if the reference is external.

The accuracy of any converter is limited by the temperature drift or long term drift of the voltage reference, even if conversion linearity is perfect. Assuming that the voltage reference is allowed to add 1/2 least significant bit error (LSB) to the converter, it is surprising how good the reference must be when even small temperature excursions are considered. When temperature changes are large, the reference design is a major problem. Table 1 shows the reference requirements for different converters while Table 2 shows how the same problems exist with digital panel meters.

The voltage reference circuitry is required to do several functions to maintain a stable output. First, input power supply changes must be rejected by the reference circuitry. Secondly, the zener used in the reference must be biased properly, while other parts of circuitry scale the typical zener voltage and provides a low impedance output. Finally, the reference circuitry must reject ambient temperature changes so that the temperature drift of the reference circuitry plus the drift of the zener does not exceed the desired drift limit.

While zener temperature coefficient is obviously critical to reference performance, other sources of drift can easily add as much error as zener — even in voltage references with modest performance of 20 ppm/ $^{\circ}\text{C}$  temperature drift. Zener drift and op amp drift add directly to the drift error, while resistor error is only a function of how well the scaling resistors track. Resistors which have a high TC can be used if they track.

For a 10V output with a 6.9V zener, the drift contribution of resistor mistracking is about 0.4 since the gain is 1.4. The range of temperature coefficient errors for different components used to make a 10V reference from a 6.9V zener are shown in Table 3. Another potential source of error, input supply variations, are negligible if the input is 1% regulated, and the resistor feeding the zener is stable to 1%.

Less frequently specified sources of error in voltage reference zeners are hysteresis and stress sensitivity. Stress on either a zener-diode junction or the series-temperaturecompensating junction will cause voltage shifts. The axial leads on discrete devices can transmit stress from outside the package to the junction, causing 1 mV to 5 mV shifts.

Temperature cycling is the discrete zener can also induce non-reversible changes in zener voltage. If a zener is heated from 25°C to 100°C and then back to 25°C, the zener voltage may not return to its original value. This is because the temperature cycle has permanently changed the stress in the die, changing the voltage. This effect can be as high as 5 mV in some diodes and may be cumulative with many temperature cycles. The new planar IC zeners, such as the LM199 (temperature stabilized) or the LM129 are insensitive to stress and show only about 50 µV of hysteresis for a 150°C temperature cycle since the package does not stress the silicon chip.

### **DESIGNING THE REFERENCE**

If moderate temperature performance such as 20 ppm/°C is all that is needed, 2 different approaches can be used in the reference design. In the first, the temperature drift error is split equally between the zener and the amplifier or scaling resistors. This requires a moderately low drift zener and op amp with 10 ppm resistors.

TABLE 1. Maximum Allowable Reference Drift for 1/2 Least Significant Bits Error of Binary Coded Converter

| TEMP<br>CHANGE | BITS |    |    |     |      |        |

|----------------|------|----|----|-----|------|--------|

|                | 6    | 8  | 10 | 12  | 14   |        |

| 25°C           | 310  | 80 | 20 | 5   | 1.25 | ppm/°C |

| 50°C           | 160  | 40 | 10 | 2.5 | 0.6  | ppm/°C |

| 100°C          | 80   | 20 | 5  | 1.2 | 0.3  | ppm/°C |

| 125°C          | 63   | 16 | 3  | 1   | 0.2  | ppm/°C |

TABLE 2. Maximum Allowable Reference Drift for 1/2 Digit Error of Digital Meters

| TEMP CHANGE | DIGITS |      |     |      |    |      |     |      |        |

|-------------|--------|------|-----|------|----|------|-----|------|--------|

|             | 2      | 21/2 | 3   | 31/2 | 4  | 41/2 | 5   | 51/2 |        |

| 25°C        | 200    | 100  | 20  | 10   | 2  | 1    | 0.2 | 0.1  | ppm/°C |

| 5°C         |        |      | 100 | 50   | 10 | 5    | 1   | 0.5  | ppm/°C |

Note 1: 0.01%/°C=100 ppm/°C, 0.001%/°C=10 ppm/°C, 0.0001%/°C=1 ppm/°C

© 1998 National Semiconductor Corporation

TABLE 3. Drift Error Contribution From Reference Components for a 10V Reference

| DEVICE                           | ERROR                  | 10V          |

|----------------------------------|------------------------|--------------|

|                                  |                        | OUTPUT DRIFT |

| Zener                            | Zener Drift            |              |

| LM199A                           | 0.5 ppm/°C             | 0.5 ppm/°C   |

| LM199, LM399A                    | 1 ppm/°C               | 1 ppm/°C     |

| LM399                            | 2 ppm/°C               | 2 ppm/°C     |

| 1N829, LM3999                    | 5 ppm/°C               | 5 ppm/°C     |

| LM129, 1N823A, 1N827A, LM329A    | 10-50 ppm/°C           | 10-50 ppm/°C |

| LM329, 1N821, 1N825              | 20-100 ppm/°C          | 20-100 ppm°C |

| Op Amp                           | Offset Voltage Drift   |              |

| LM725, LH0044, LM121             | 1 μV/°C                | 0.15 ppm/°C  |

| LM108A, LM208A, LM308A           | 5 μV/°C                | 0.7 ppm/°C   |

| LM741, LM101A                    | 15 μV/°C               | 2 ppm/°C     |

| LM741C, LM301A, LM308            | 30 μV/°C               | 4 ppm/°C     |

| Resistors                        | Resistance Ratio Drift |              |

| 1% (RN55D)                       | 50-100 ppm             | 20-40 ppm/°C |

| 0.1% (Wirewound)                 | 5–10                   | 2-4 ppm      |

| Tracking 1 ppm Film or Wirewound | _                      | 0.4 ppm/°C   |

The second approach uses a very low drift zener and allows the buffer amplifier or scaling resistor to cause most of the drift error. This type of design is now made economical by the availability of low cost temperature stabilized IC zeners with virtually no TC. Further, the temperature coefficient of this reference is easily upgraded, if necessary. The 2 reference circuits are shown in *Figure 1* and *Figure 2*.

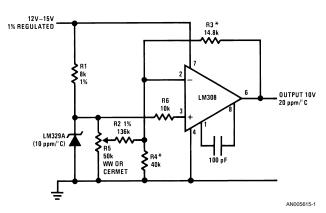

In Figure 1, an LM308 op amp is used to increase the typical zener output to 10V while adding a worst-case drift of 4 ppm/°C to the 10 ppm/°C of the zener. Resistors R3 and R4 should track to better than 10 ppm bringing the total error so far to 18 ppm. Since the output must be adjusted to eliminate the initial zener tolerance, a pot, R5 and R2 have been added. The loading on the pot by R2 is small, and there is no tracking requirement between the pot and R2. It is necessary for R2 to track R3 and R4 within 50 ppm.

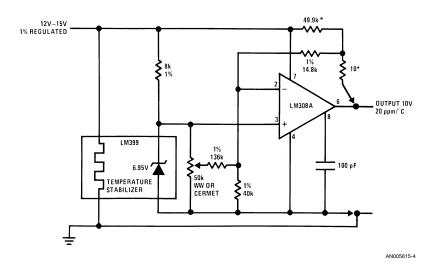

In Figure 2, a low drift reference and op amp are used to give a total drift, exclusive of resistors of 3 ppm/°C. Now the resistor tracking requirement is relaxed to about 50 ppm, allowing ordinary 1% resistors to be used. The circuit in Figure 2 is modified easily for applications requiring 3 ppm/°C to 5 ppm/°C overall drift by tightening the tracking of the resistors. For more accurate applications, the Kelvin sensing for both output and ground should be used. For even lower drifts, substituting a 1  $\mu$ V/°C op amp, 1 ppm tracking resistors and an LM199A zener, overall drifts of 1 ppm/°C can be achieved. In both of the circuits, it is important to remember that the tracking of resistors can, at worst-case, be twice temperature drift of either resistance.

In both circuits, the zener is biased by a single resistor from the supply, rather than from the reference output. This eliminates possible start-up problems and, because of the  $1\Omega$  dynamic impedance of the IC zeners, only adds about 20 µV of error. Compensation for input changes is shown in Figure 2. Conventional zeners do not allow this biasing. A conventional 5 ppm reference such as the 1N829 has a dynamic impedance of about 15 $\Omega$ . If it is biased from a resistor from a 1% regulated 15V supply, the operating current can change by 1.7% or 127  $\mu A$ . This will shift the zener voltage by 1.9 mV or 60 ppm. With the IC zeners operating at 1 mA, a 1% shift in the supply will change the reference by 20 µV or 3 ppm. Further, power dissipation in the IC is only 7 mW, giving low warm-up drift compared to 7.5 mA zeners. The biasing resistor for the IC zener need not be any better than an ordinary 1% resistor since performance is independent of current.

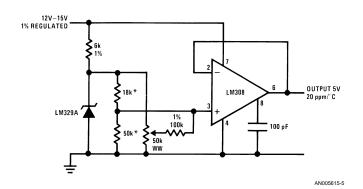

When output voltages less than the zener voltage are desired, the IC zeners significantly simplify circuit design since no auxiliary regulator is needed for biasing. Figure 3 shows a 5V reference circuit for use with a 15V input. In this case, zener drift contributes proportionally to the output drift while op amp offset drift adds a greater rate. With the 10V reference, 15  $\mu\text{V/}^{\prime}\text{C}$  from the op amp contributed 2 ppm/ $^{\prime}\text{C}$  drift, but for the 5V reference, 15  $\mu\text{V/}^{\prime}\text{C}$  adds 3 ppm/ $^{\prime}\text{C}$ . This makes op amp choice more important as the output voltage is lowered. Of course, if a high output impedance is tolerable, the op amp can be eliminated.

FIGURE 1. 10V, 20 ppm Reference Using a Low Cost Zener and Low Drift Resistors

$^{*}$ Optional — improves line regulation

FIGURE 2. 10V Reference has Low Drift Reference and Standard 1% Resistors. Kelvin Sensing is Shown with Compensation for Line Changes.

\*20 ppm tracking

FIGURE 3. Low Voltage Reference

#### APPROACHING THE ULTIMATE DRIFT

To obtain the lowest possible drifts, temperature coef-ficient trimming is necessary. With discrete zeners, the operating current can sometimes be trimmed to change the TC of the reference; however, the temperature coefficient is not always linear or predictable. With the new IC zeners, TC is independent of operating current so trimming must be done elsewhere in the circuit. The lowest drift components should be used since trimming can only remove a linear component of

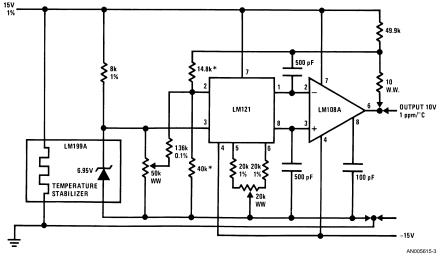

drift. High TC devices can have a highly non-linear drift, making trimming difficult. Figure 4 shows a circuit suitable for trimming. An LM199A reference with 0.5 ppm/°C drift is used with a 121/108 op amp. Resistors should be 1 ppm tracking to give overall untrimmed drifts of about 0.9 ppm. The 121/108 is a low drift amplifier combination where drift is predictably proportional to offset voltage. An offset can be set for the 108/121 combination to cancel the measured drift with 1 pass calibration.

\*1 ppm tracking

FIGURE 4. Ultra Low Drift Reference

Trimming procedure is as follows: the zener is disconnected and the input of the op amp grounded. Then the offset of the op amp is nulled out to zero. Reconnecting the zener, the output is adjusted to precisely 10V. A temperature run is made and the drift noted. The op amp will drift 3.6  $\mu\text{V/}^{\circ}\text{C}$  for every 1 mV of offset, so for every 5  $\mu\text{V/}^{\circ}\text{C}$  drift at the output, the offset of the op amp is adjusted 1 mV (1.4 mV measured at the output) in the opposite direction. The output is readjusted to 10V and the drift checked.

Although this trimming scheme was chosen since only a single adjustment is usually required, compensation is not always perfect. Hysteresis effects can appear in resistors or op amps as well as zeners. Best results can be obtained by cycling the circuit to temperature a few times before taking data to relieve assembly stresses on the components. Also,

oven testing can sometimes cause thermal gradients across circuits, giving 50  $\mu$ V to 100  $\mu$ V of error. However, with careful layout and trimming, overall reference drifts of 0.1 ppm/°C to 0.2 ppm/°C can be achieved.

There are 2 other possible problem areas to be considered before final layout. Good single point grounding is important. Traces on a PC board can easily have  $0.1\Omega$  and only 10 mA will cause a 1 mV shift. Also, since these references are close to high-speed digital circuitry, shielding may be necessary to prevent pick-up at the inputs of the op amp. Transient response to pick-up or rapid loading changes can sometimes be improved by a large capacitor. (1  $\mu F - 10~\mu F)$  directly on the op amp output; but this will depend on the stability of the op amp.

Book Extract End

PrintDate=1998/05/15 PrintTime=14:18:38 40974 an005615 Rev. No. 3 cmserv **Proof**

5

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**AN-184**

National Semiconductor Corporation

Americas Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor

Europe Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80 National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5620-6175 Fax: 81-3-5620-6179

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.